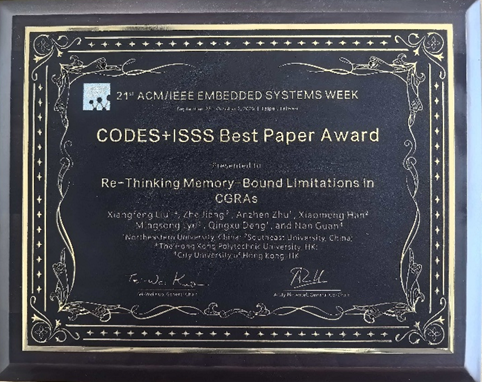

近日,计算机学院邓庆绪教授团队在可重构计算架构优化方向的最新研究成果被嵌入式系统领域国际顶级会议CODES+ISSS 2025录用,并荣获最佳论文奖(Best Paper Award)。CODES+ISSS(International Conference on Hardware/Software Codesign and System Synthesis)是嵌入式系统领域最具影响力的国际学术会议之一,专注于硬件软件协同设计与系统综合创新,在学术界和工业界享有盛誉。会议论文代表着嵌入式系统领域的前沿突破方向,对推动该领域技术发展具有重要引领作用。

论文:Re-thinking Memory-Bound Limitations in CGRAs**

作者:刘向峰、江哲、朱安震、韩晓萌、吕鸣松、邓庆绪、关楠

第一单位:东北大学,合作单位:香港城市大学、东南大学

该工作聚焦粗粒度可重构阵列(CGRA)这一新兴专用加速器架构,针对其在处理图神经网络、科学计算、数据分析等新兴应用时面临的严峻内存瓶颈问题展开深入研究。传统CGRA架构在面对大规模数据和复杂访存模式时,往往因内存系统设计局限导致计算资源严重闲置,加速效能难以充分发挥。论文创新性地提出了面向CGRA的新型内存架构设计方法论,通过重新审视和突破传统设计范式,系统性解决了制约CGRA广泛应用的核心技术难题。

研究团队提出的解决方案包含三个层次的协同创新:在架构层面,设计了新型混合存储层次结构,在大幅降低存储开销的同时有效支撑海量数据处理需求;在机制层面,创造性地引入了适配CGRA执行特性的智能预取策略,将硬件空闲时间转化为性能提升的契机;在优化层面,开发了基于访存行为特征的动态资源调配技术,实现了对异构计算负载的精准适配。这些创新相互协同,构成了一套完整的技术体系。

实验结果表明,该方案在保持极低硬件开销的前提下,显著提升了CGRA在多种实际应用场景中的加速性能,成功突破了长期制约可重构架构发展的内存墙瓶颈。这一成果不仅为CGRA架构研究开辟了新方向,也为其他领域专用加速器的设计提供了重要借鉴。

该成果凝聚了团队长期的技术积累与深入探索,在理论创新与工程实践两个维度都取得了重要突破。团队正在此基础上推进系列后续研究工作,并积极探索产学研合作机会,致力于将研究成果转化为推动智能计算基础设施演进的实际生产力。